# **SYNOPSYS**<sup>®</sup>

Our Technology, Your Innovation™

### Emerging Technologies for Computing Paradigm Shift

Brandon Wang VP, Corporate Technology Strategy

### **SYNOPSYS**<sup>®</sup>

Our Technology, Your Innovation"

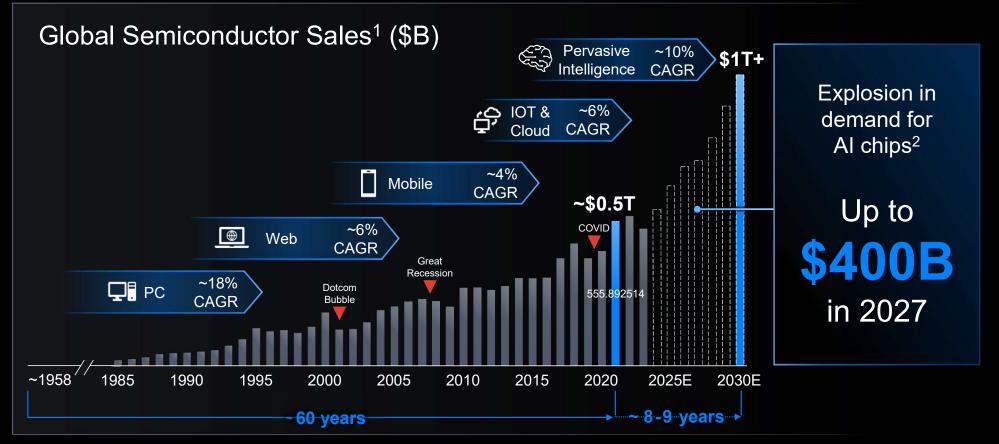

### Sharp Acceleration in Semiconductor Demand

1. Sources: SIA/WSTS (historicals); forecasts based on Gartner, TechInsights, IBS, SIA/WSTS and consensus analyst forecasts for leading semiconductor companies

2. Sources: Gartner, AMD, Nvidia, Intel, Goldman Sachs

synopsys<sup>®</sup>

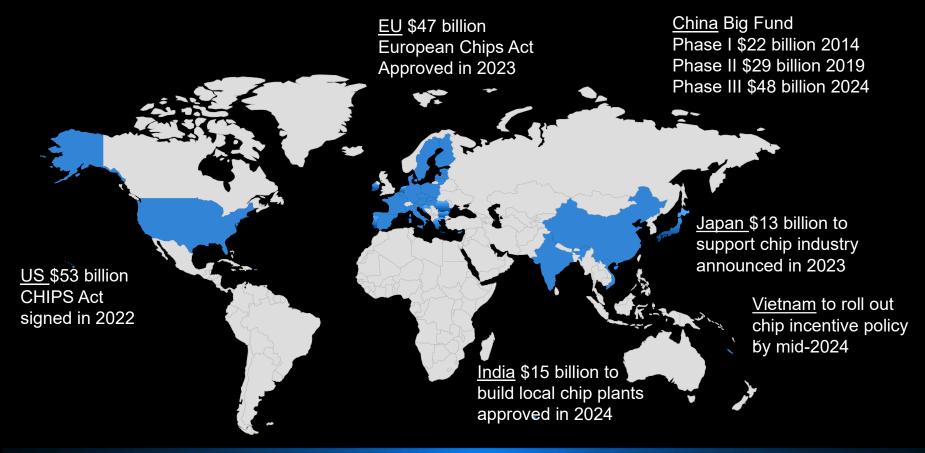

### **Great Time for Chip Industry**

#### VC-backed Chip Startups Closed 175 Deals, Raised \$5.3 Billion in 2024 1H

**Synopsys**®

#### 1011 0100

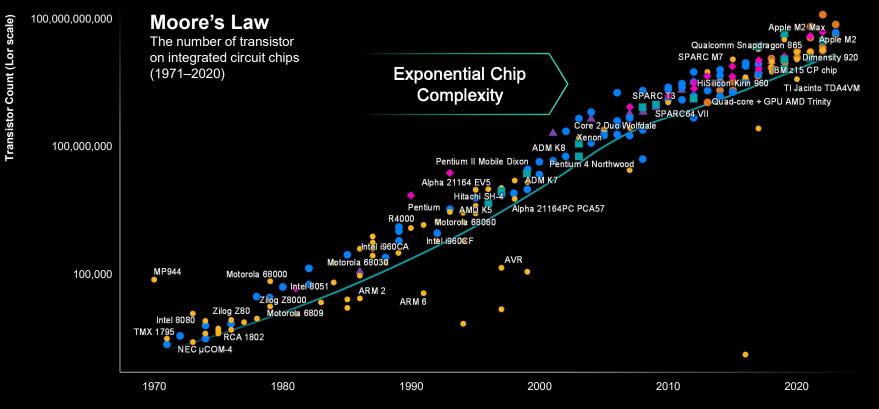

### $\frac{1}{2}$ Transistors are NOT getting more efficient, Pushing the Limits of Chip Design

Source: Wikipedia – Transistor Count: https://interludeone.com/posts/2021-04-21-chips/chips\_files/figure-html/unnamed-chunk-4-1.png

#### synopsys\*

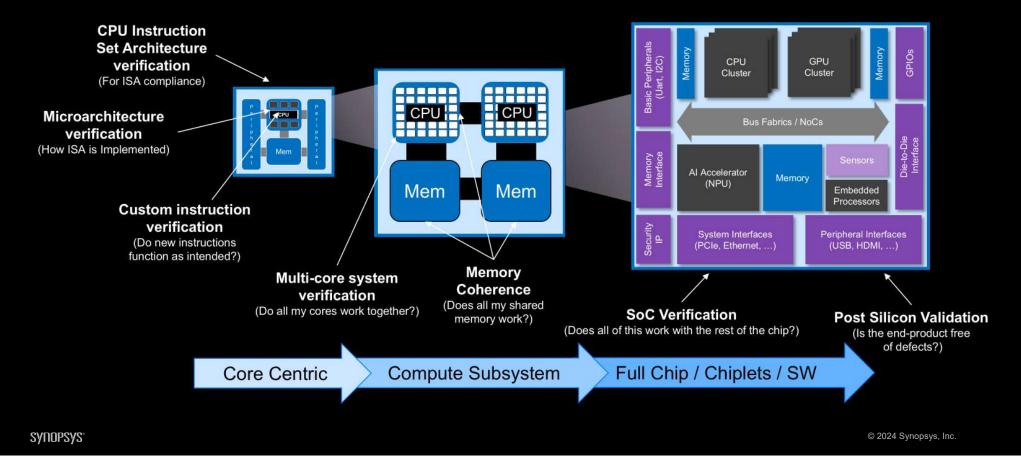

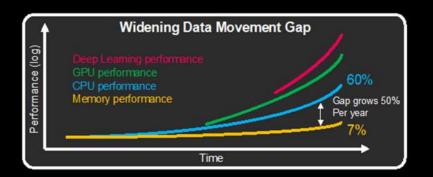

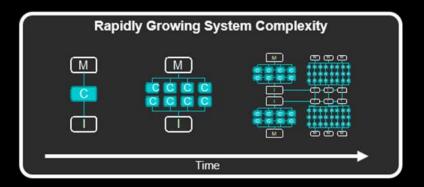

#### Customer Problem Scope Is Rapidly Getting Complex

From ISA through CPU, arrays of CPUs and Systems on Chips / of Chiplets

#### 1011 0100

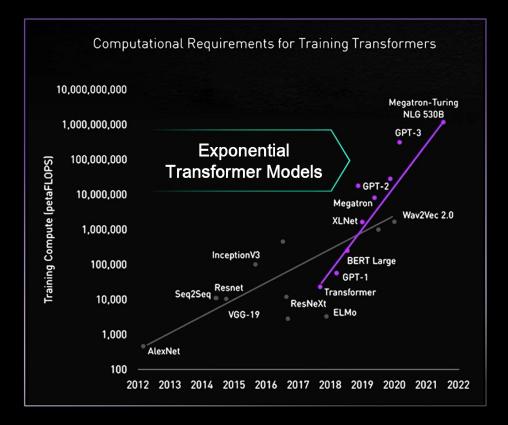

### Newer Models Further Pushing Limits of Compute

### All Models Excluding Transformers: 8X / 2 years

Transformer AI Models: 275X / 2 years

Context-Aware Transformer Models Come at a Price

synopsys°

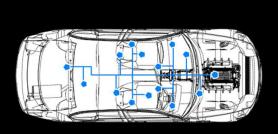

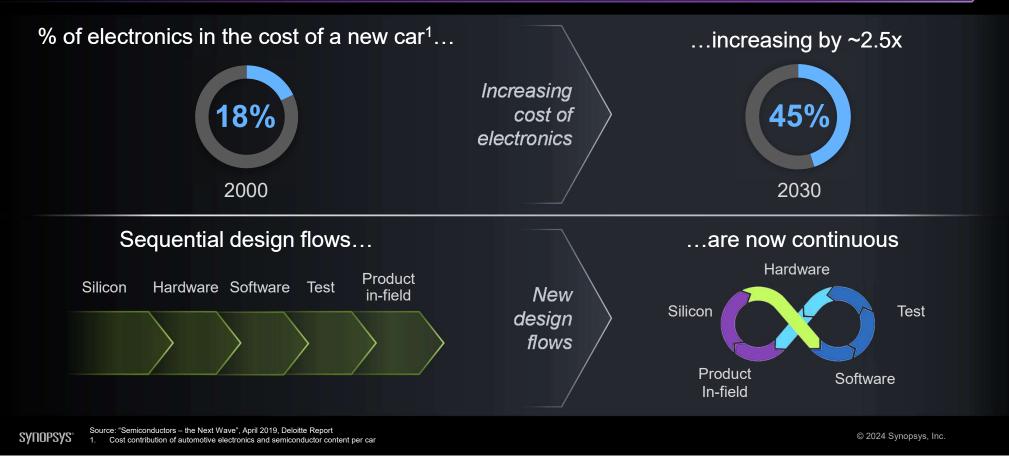

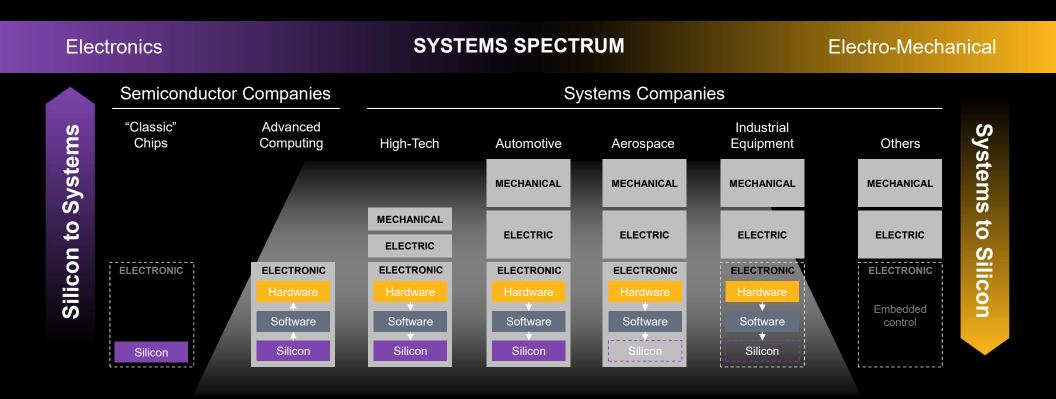

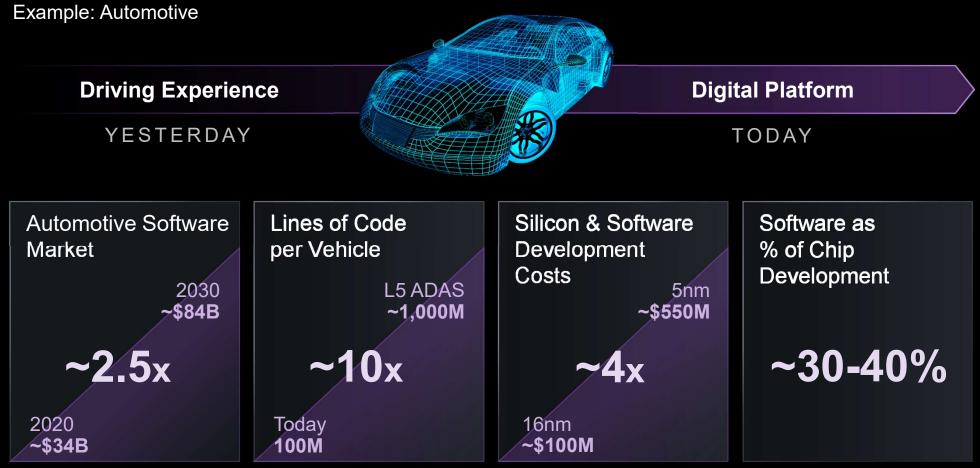

### Increasing Silicon and Software Content In Systems Products

Autonomy and software-defined systems reshaping industries

Systems companies re-architecting products, business models and development processes

Driving demand for massive compute, both at the edge and the data center

#### Systems R&D Processes Are More Complex, More Costly

#### TODAY

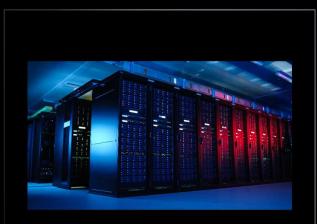

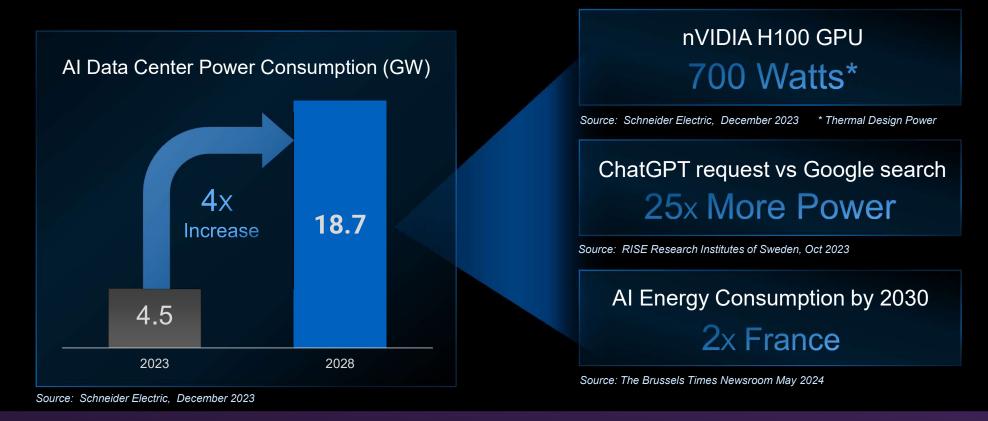

### AI Driving Unprecedented Power Consumption

Software to Device Solution Needed to Address the Magnitude of Power Consumption

### Huge Amount of Water Usage is Also UNSUSTAINABLE

#### Current Cooling Solutions room-temperature liquid colling

- HPC environments moving from hybrid air-liquid cooling to just liquid cooling @ higher flow rates

- This solution will not be enough to maintain system temperature and functionality

- Due to expensive packaging for high power dissipation capabilities

Google's Global Data Center in 2021 Water Usage 4.3 Billion Gallons

Source: Google, 2022

Frontier (#1 most powerful supercomputer) liquid-cooled ~6,000 gallons per minute

Source: Bloomberg, 2023

Innovative Cooling Solutions Needed to Address the Unsustainability of Water Usage

# The era of **PERVASIVE INTELLIGENCE**

#### Artificial Intelligence

Exponential productivity and efficiency gains

Silicon Proliferation

More silicon content everywhere

#### Software-Defined Systems

New applications, new methodologies

#### **Silicon to Systems Design Solutions**

New design paradigm; Solving Energy challenges while addressing complexity

### Emerging Technologies Addressing the Challenges in the Era of Pervasive Intelligence

#### Silicon Complexity

The need for custom silicon and the growing complexity of chip design

#### Silicon & Systems Intersection

Growing at the intersection of hardware and software

#### Compute & Energy Limits

Enhance compute power and be sustainable

### Silicon Complexity

### **Customers Adopting New Design Paradigms in Computing**

#### Optimal mix of Compute type per Workload

| CPU | GPU | AI | FPGA | Accelerator |

|-----|-----|----|------|-------------|

|     |     |    |      |             |

|     |     |    |      | Abb dist    |

#### Fabric + Cache Innovations to Accelerate Data

|  | 9999<br>99<br>6666 |  |  |  |

|--|--------------------|--|--|--|

|--|--------------------|--|--|--|

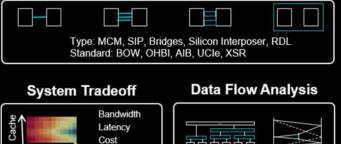

#### **Careful Optimizations of Chiplet Interface**

Power

Topology

Source: Baya Systems, 2024

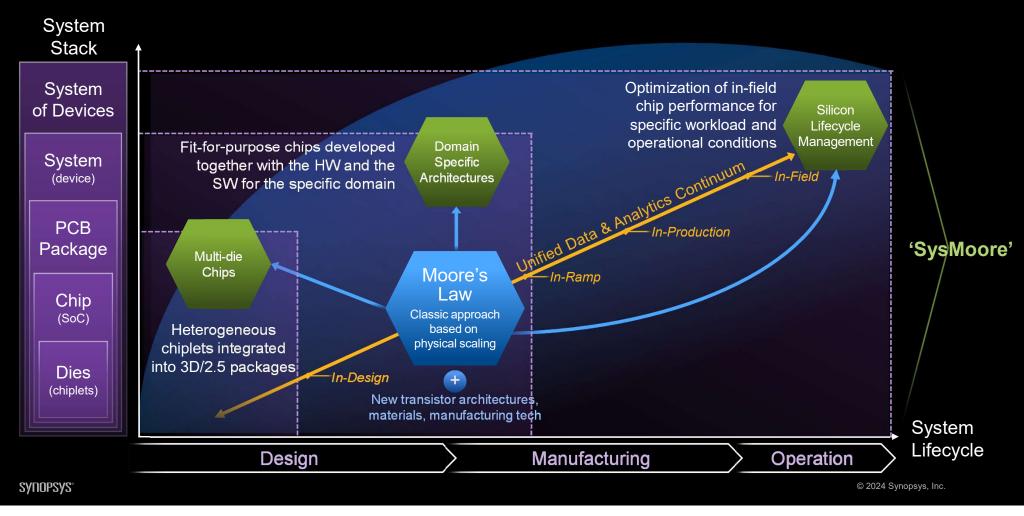

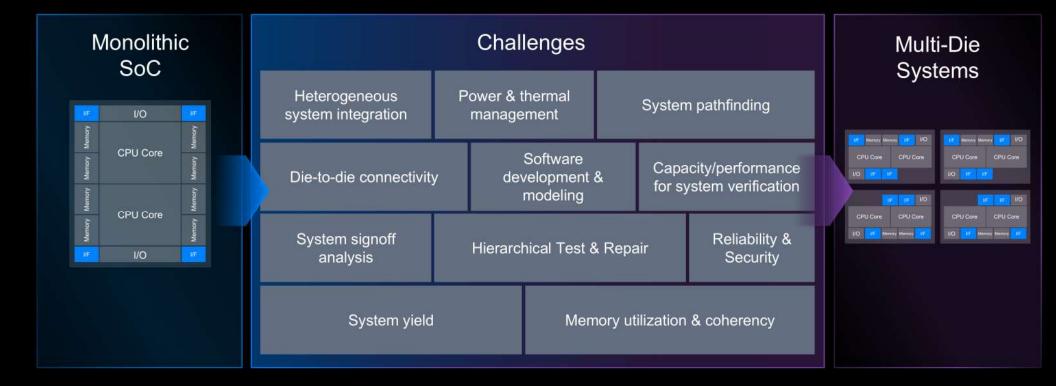

### Meeting Explosive Compute Demand Requires New Paradigm

### Heterogeneous Systems Design Challenges

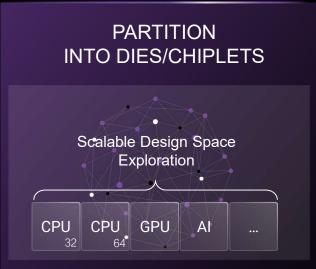

### Early Architecture Exploration For Multi-Die Systems

Partitioning & Optimization to Accelerate Architecture Realization with Platform Architect

Separate system into its functions, scale functions across multiple dies

Meet scaling, fabrication, and functionality requirements

#### OPTIMIZE MULTI-DIE SYSTEM

Model-Based Architectural Exploration of Multi-die Systems

Optimize for bandwidth density, energy per bit, cost and latency

Select chip-to-chip protocols and interfaces: UCIe, PCIe, CXL, ...

#### ACCELERATE ARCHITECTURE REALIZATION

Enable silicon, package and software teams with multi-die system analysis

Leverage die-on-die and die-to-die IP models

**SYNOPSYS**°

### Silicon & System Intersection

### Silicon to Systems Transition Ongoing Across Verticals

### Products Are Becoming SW Platforms In Every Industry

Source: Automotive Software and Electronics 2030 (McKinsey, Jul 2019); Levers to Unleash Value (Volkswagen, Jan 2020); Computer on Wheels (Roland Berger, Q1 2020)

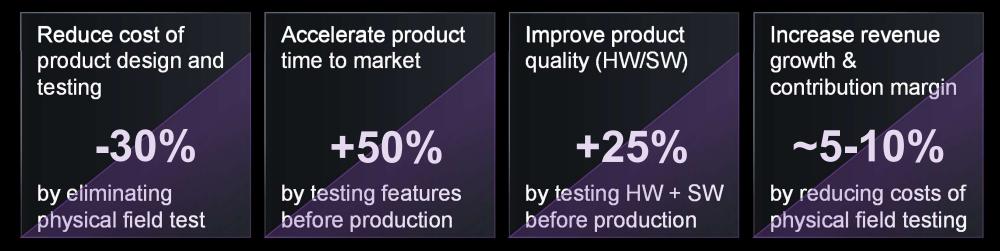

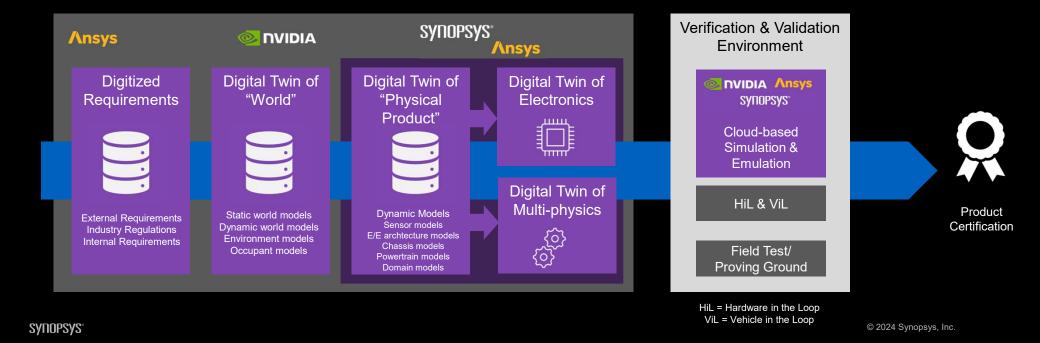

### Digital Twins Will Revolutionize CAE for Product Development

### Digital Twin A dynamic <u>virtual</u> model of a <u>physical</u> product

Expected Customer Benefits<sup>1</sup>

Source: Digital twins: The Art of the Possible in Product Development and Beyond (McKinsey, Apr 2022)

1. Percentage increases represent a comparison between without and with digital twin

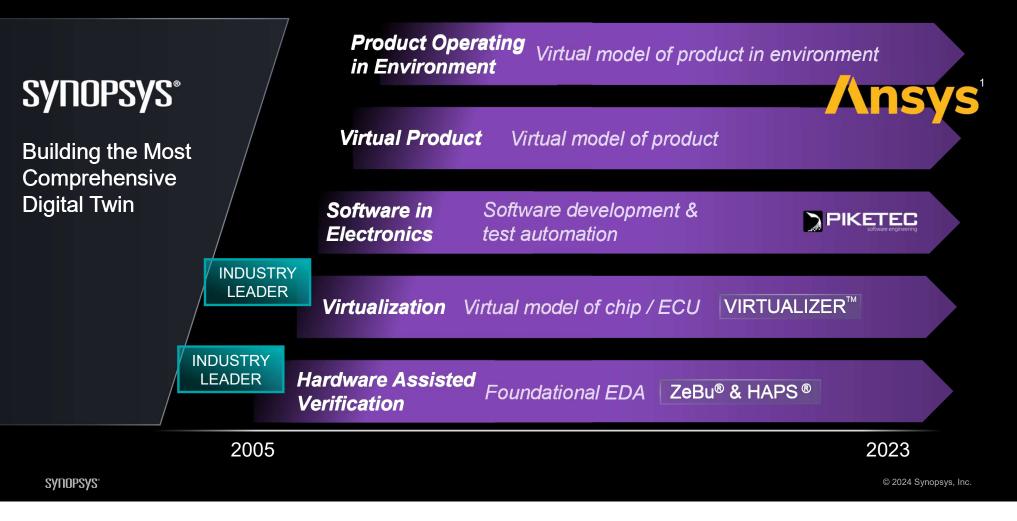

### Most Comprehensive System Virtualization Solution Portfolio

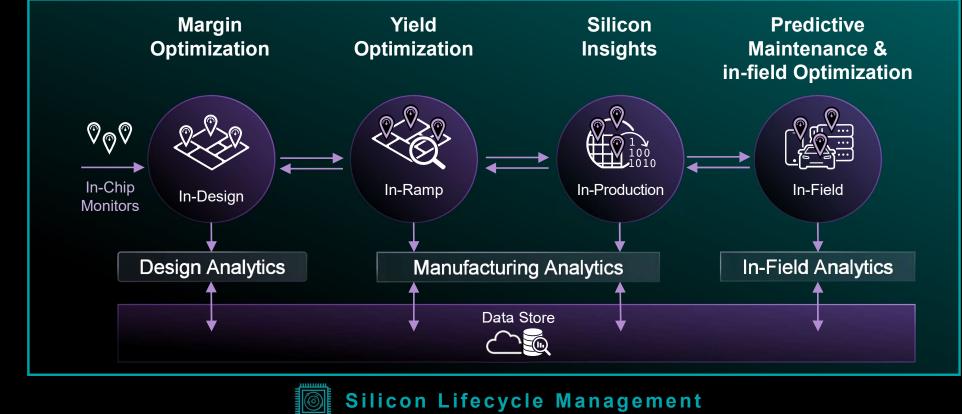

### ...Including Silicon Lifecycle Management Innovation

Monitoring and optimization of relevant chip metrics across lifecycle stages

**Synopsys**®

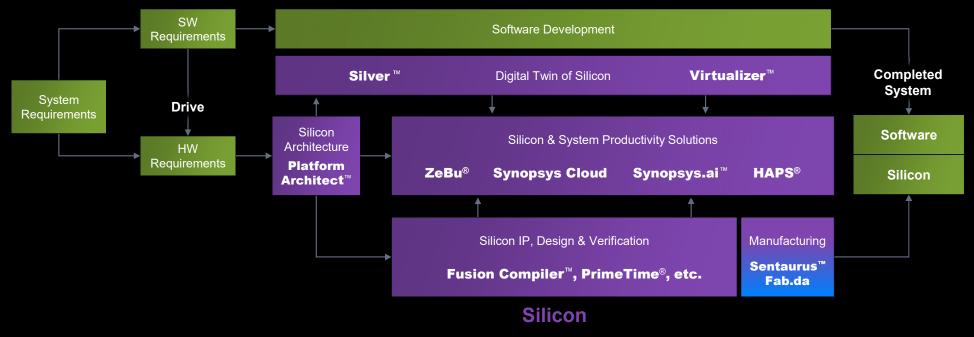

### Holistic Silicon to Systems Design Solutions

Customer Synopsys Partner

#### Software

Addressing complexity and accelerating systems design cycles

synopsys<sup>®</sup>

### Next-Generation Product Development with Digital Twins

Real world

Product under development

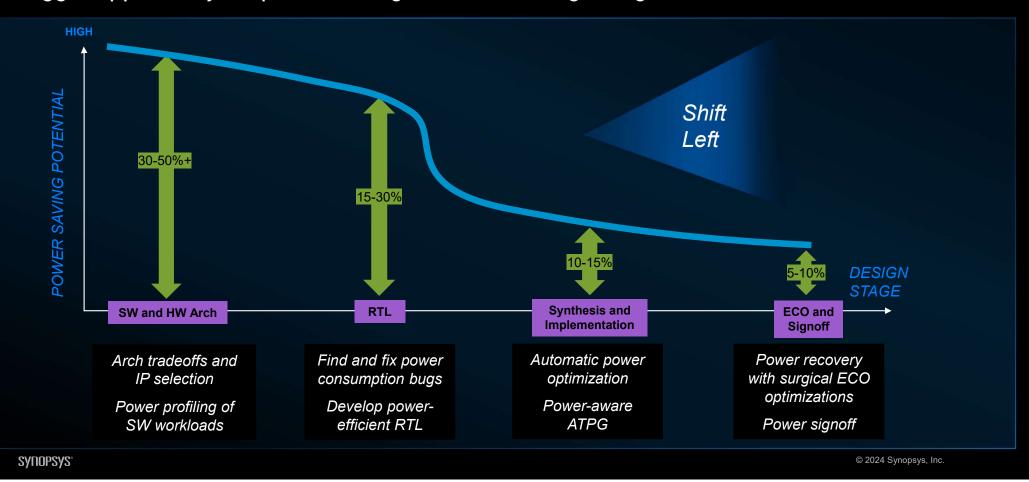

### Compute & Energy Limits

#### Shift-Left Is a Must for Low Power and Energy Efficiency Bigger opportunity for power savings at earlier design stages

## SLMs a Potential Paradigm Shift in the Al Landscape LLMs remain for a broader applications, SLMs offer for specialized solutions

|                       | <b>LLM</b><br>(Large Language Model)                                                                        | <b>SLM</b><br>(Small Language Model)                                                                                               |

|-----------------------|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Definition            | A language model with a very large number of parameters and high complexity.                                | A language model with fewer parameters and less complexity.                                                                        |

| Example               | GPT-4                                                                                                       | Llama 3 8B, phi-3, Mistral, Gemma                                                                                                  |

| Model Size            | GPT-4 around 1.76 trillion parameters                                                                       | e.g., Llama 3 8B, 8 billion parameters                                                                                             |

| Application           | Ideal for complex applications requiring deep language understanding, generation, and high performance.     | Specific tasks and environments, requiring<br>much lesser reasoning and creation, like<br>coding, translation, summarization, etc. |

| Energy<br>Consumption | Higher energy consumption due to<br>extensive computational requirements and<br>large-scale infrastructure. | Lower energy consumption due to simpler computations and smaller model size.                                                       |

| synopsys <sup>®</sup> |                                                                                                             | © 2024 Synopsys, Inc.                                                                                                              |

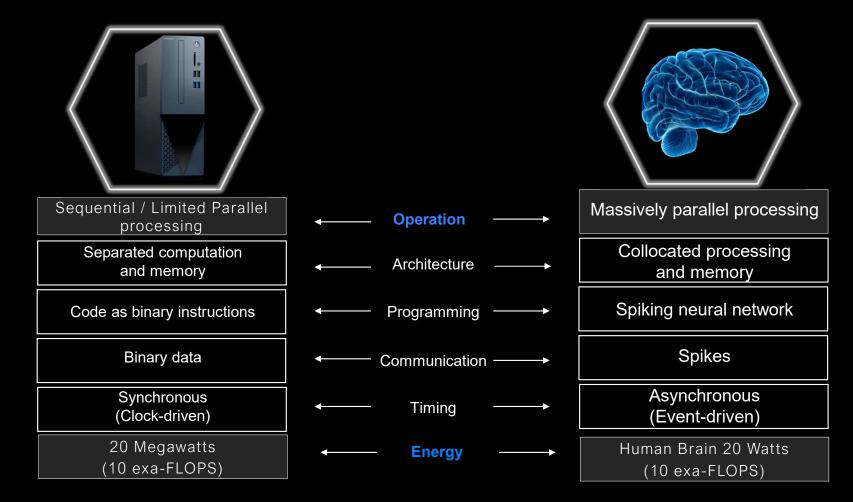

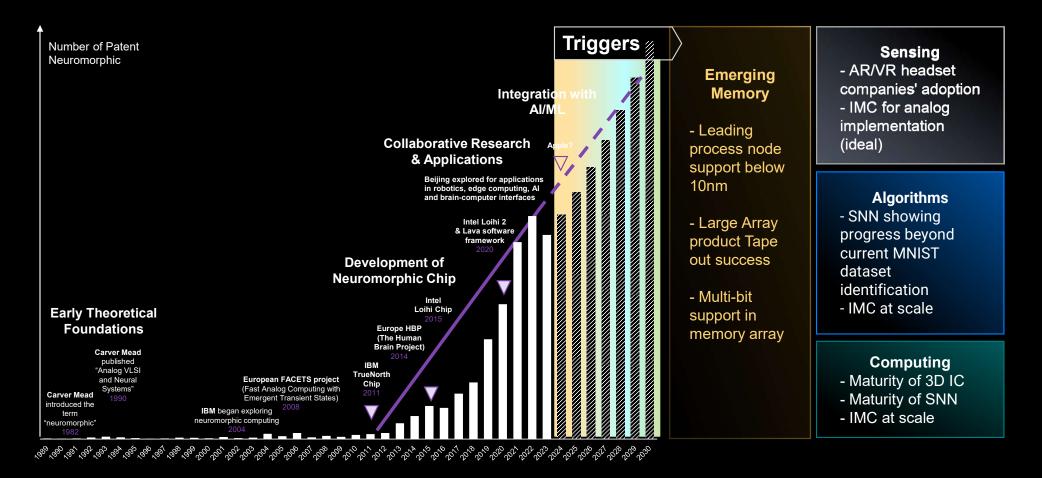

### Neuromorphic Computing: Supercharged but Energy Efficient

**Synopsys**®

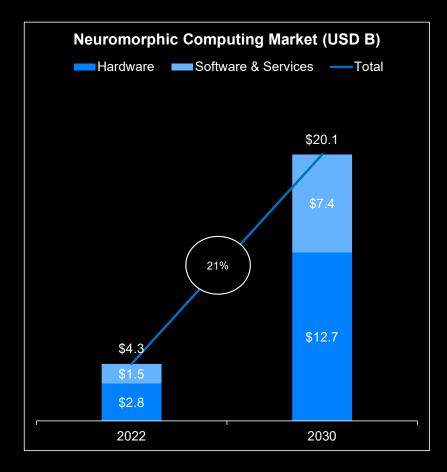

### Recent Advances Put Neuromorphic Computing within Reach

#### ✓ Key Movers' Efforts

- Intel has built the world's largest neuromorphic system Hala Point (2024), and utilizes Intel's Loihi 2 processor, which is made using the Intel 4 process and has 128 cores per chip. Each chip includes up to 1 million digital neurons and 120 million synapses.

- IBM's TrueNorth chip has over 1 million neurons and over 256 million synapses. NorthPole (2023) is the next generation of TrueNorth at 12nm

#### ✓ Great Promise to Several Application

Image processing, data processing, and object detection will grow by over 20% CAGR from 2022 to 2030, and penetrate many end markets, such as industrial IoT, automotive, AR/XR, security and surveillance.

#### ✓ Academic Achievements

**Carver Mead's** pioneering work laid the foundation for brain-inspired systems by demonstrating how silicon circuits could mimic neurobiological processes. Carried forward by his student **Professor Kwabena Boahen**.

#### ✓ Scientific Progress

There are surging neuromorphic patents. 899 patents were granted in 2023. Technical papers significant increased, 8,104 papers were published in 2023.

#### ✓ Government Funding & Project

DARPA SyNAPSE project and the EU Human Brain Project

### Neuromorphic Computing Four-Segment Development

|            | Key Technologies                                 | Key Challenges                                                                                                                                                                      | Estimated Time to<br>Tech Readiness |

|------------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| SENSING    | Neuromorphic sensors<br>In-sensor computing      | <ul> <li>Ideal implementation is analog and mixed signal<br/>or asynchronous digital designs – challenging to<br/>implement at scale</li> </ul>                                     | < 3 Years                           |

| ALGORITHEM | Computing using Spiking<br>Neural Networks (SNN) | <ul> <li>Training challenges due to limited back propagation</li> <li>Inefficiency in encoding spikes</li> <li>Scaling difficult (asynchronous or analog implementation)</li> </ul> | > 5 Years                           |

| COMPUTING  | Neuromorphic Electronics                         | <ul> <li>Ideal implementation is analog and mixed<br/>signal with SNN</li> <li>Data Communication bottlenecks</li> </ul>                                                            | > 5 Years                           |

| ۶          | ReRAM                                            | <ul><li>One-bit to multiple</li><li>Shrink down to lower node</li><li>High voltage to write</li></ul>                                                                               | 3-5 Years                           |

| MEMORY     | MRAM                                             | <ul> <li>Retention failures due to an<br/>inherent thermal instability</li> <li>Manufacturing challenge</li> </ul>                                                                  |                                     |

|            | FeFET                                            | Short data retention time                                                                                                                                                           | >5 Years                            |

### **Emerging Memory: The Key to Neuromorphic Computing**

#### **Synopsys**®

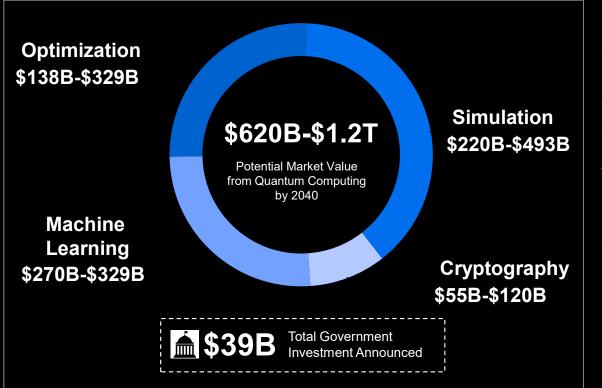

### Quantum Leap: Beyond Classical Computing

"Quantum computers rely on encoding information in a fundamentally different way than classical computers."

-William Oliver, Director, MIT Center for Quantum Engineering | Professor, MIT EECS

| Classical Computer           |                                                                                                                                                                                                    | Quantum Computer                                                                                                                                                                                                                                     |  |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Fundamental<br>logic element | "Bit" : classical bit<br>(transistor, spin in magnetic memory,)                                                                                                                                    | "Qubit" : quantum bit<br>(any coherent two-level system)                                                                                                                                                                                             |  |

| State                        | 0 "Or" 1                                                                                                                                                                                           | $ 0\rangle \qquad Superposition: \\ \alpha 0\rangle + \beta 1\rangle \\  0\rangle \qquad \text{``And''}   1\rangle \\  \psi\rangle = \alpha \begin{bmatrix} 1 \\ 0 \end{bmatrix} + \beta \begin{bmatrix} 0 \\ 1 \end{bmatrix}$                       |  |

| Measurement                  | <ul> <li>Discrete states</li> <li>Deterministic measurement:<br/>Ex: Set as 1, measure as 1</li> </ul>                                                                                             | <ul> <li>Superposition states</li> <li>Probabilistic measurement:<br/>Ex: If  α  =  β , 50%  0⟩, 50%  1⟩</li> </ul>                                                                                                                                  |  |

| Fundamental<br>logic element | "Bit" : classical bit<br>(transistor, spin in magnetic memory,)                                                                                                                                    | "Qubit" : quantum bit<br>(any coherent two-level system)                                                                                                                                                                                             |  |

| Computing                    | <ul> <li>N bits: One N-bit state</li> <li>000, 001,, 111 (N = 3)</li> <li>Change a bit: new calculation (classical parallelism)</li> <li>○○○ → □○○ → €(○○○)</li> <li>○○1 → □○○ → €(○○1)</li> </ul> | • N qubits: $2^{N}$ components to one state<br>$\alpha  000\rangle + \beta  001\rangle + \dots + \gamma  111\rangle$ (N = 3)<br>• Quantum parallelism & interference<br>$\alpha  000\rangle + \beta  001\rangle + \dots + \beta  111\rangle$ (N = 4) |  |

SYNOPSYS\* Source: MIT, Qubit Counter

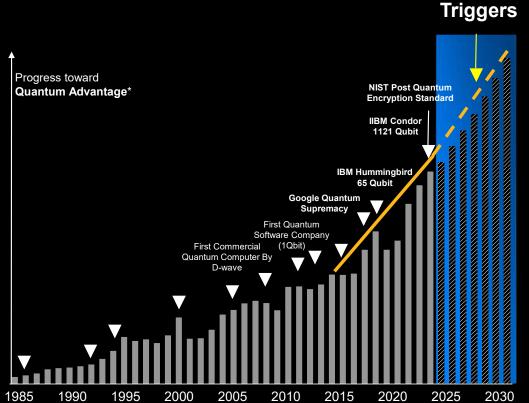

### Quantum Computing Development Accelerating

Source: McKinsey, BCG

#### ✓ Technological Breakthroughs

IBM unveiled the 1,121 qubits and updated its road map to develop a 4,000+ qubit processor in 2025

#### ✓ Scientific Progress

There are surging quantum patents. 16,731 patents were granted in 2023. Quantum papers flat, 111K papers were published in 2023. The papers focus on Quantum Design Automation are on the rise

#### ✓ Increasing Investment Flows

More than \$5B invested in Quantum Computing by VCs since 2019, equals to above 85% of all VC investments

#### Abundant Government Funding

Governments funding is a major force driving R&D efforts. US has already committed \$3.8 billion

#### Hyperscalers and Large Semi Companies All-In on Quantum Computing

Multiple billion dollars are committed by 2029

synopsys<sup>®</sup>

### Quantum Takeoff: Potential Ignition Points

#### Usage to address substantial real-world problems • Evident scaling of readout circuit technology, using ٠ either multiplexing or optical Profitable business model for Quantum Computing ٠ presented by a company or partner Consistent or reducing energy demand per qubit ٠ 10:1 error code correction ratio ٠ Full fault tolerant Quantum computer • 100,000 qubit quantum computer • First commercial application •

\* Quantum advantage: refers to the demonstrated and measured success to process a real-world problem faster on a quantum computer than on a classical computer

#### Synopsys\*

#### Quantum Design Automation (QDA) Stack: Navigating Complex Challenges

|           | Stack                      | Definition                                                                                     | Key Challenges                                                                                                                                                      |

|-----------|----------------------------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | Modeling                   | Atomistic modeling, parametric extraction, and simulation of quantum devices                   | Extensive modeling and incorporation of all relevant quantum effects across various operating corners                                                               |

|           | Simulation<br>(Emulation)  | Replication of quantum behavior for testing and development                                    | Scalability to large numbers of qubits due to limited memory                                                                                                        |

|           | Synthesis                  | Building and optimization of quantum algorithms for specific tasks                             | Data encoding is expensive<br>Data encoding is also sensitive to noise                                                                                              |

| QDA       | Compilation                | Translation of quantum code to run on specific hardware setups                                 | Compilation needs to be hardware aware to choose the implementation that minimizes faults                                                                           |

|           | Verification/Testing       | Confirmation of accuracy and functionality of quantum algorithms and designs                   | Verifying complex algorithm, such as Harrow-<br>Hassidim-Lloyd algorithm and the Binary Welded Tree<br>quantum walk algorithm, remain difficult                     |

|           | Schematic<br>Editor/Layout | Creation and modification of quantum circuit designs                                           | Quantum computers haven't reached the scale that necessitates optimized automation solutions                                                                        |

|           | Error Control              | Identification and correction of noise errors in quantum computation processes                 | Error correction schemes add additional overhead ,but are required to unlock quantum full potential                                                                 |

| IP        | Control Circuit            | Manages quantum processes using<br>CMOS, FPGA, or Josephson junctions for<br>precision control | Implementing Cryo/Cold CMOS at advanced nodes<br>presents significant challenges<br>Lack of a Process Design Kit (PDK) at 22nm poses a<br>constraint to scalability |

| synopsys° |                            |                                                                                                | Technical Hurdles © 2024 Synopsys, Inc.                                                                                                                             |

### Synopsys Technology Intelligence Center (TIC)

37 Emerging Technologies under 8 Categories

Collaboration, Partnership, Investment

Synopsys

Our Technology, Your Innovation"

# THANK YOU